MAKE A MEME

View Large Image

| View Original: | DRAM.svg (400x400) | |||

| Download: | Original | Medium | Small | Thumb |

| Courtesy of: | commons.wikimedia.org | More Like This | ||

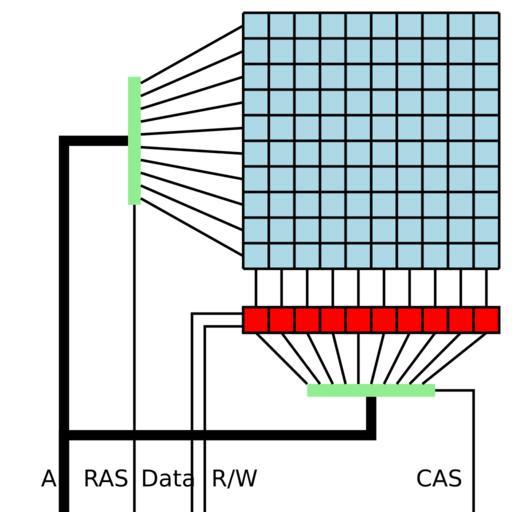

| Keywords: DRAM.svg Organization of a semiconductor Dynamic RAM DRAM chip Each bit of data is stored a memory cell The cells blue blocks are laid out in an array of rows and columns on the chip The memory address applied to the chip A is broken into two parts; a row address which is decoded by a row address decoder green rectangle left to select one row of cells and a column address which is decoded by a column address decoder green rectangle bottom to select one of the cells in the active row When the Row Address Strobe RAS line is asserted the row of memory cells is activated transferring the bit of data in each cell to the sense amplifiers red blocks When the Column Address Strobe CAS line is asserted the column address decoder picks the bit from one column to output on the Data line <br /> The write process is similar except that the Read/Write R/W line is asserted so instead of reading a bit a bit of data on the Data line is written by the selected sense amplifier into the memory cell Own 2008-03-05 HandigeHarry PD ImageNote 1 189 7 205 206 400 400 2 Memory cells ImageNoteEnd 1 ImageNote 2 91 46 26 124 400 400 2 Row address decoder ImageNoteEnd 2 ImageNote 3 182 228 216 44 400 400 2 Sense amplifiers ImageNoteEnd 3 ImageNote 4 231 291 121 27 400 400 2 Column address decoder ImageNoteEnd 4 DRAM 10x10 arrays | ||||